SPECIAL REPORT Avoid 4 Common Pitfalls of Designing an OpenVPX™ System

# To Avoid the 4 Most Common OpenVPX Design Pitfalls, YOU MUST LEARN...

- **\*1** Why VPX<sup>TM</sup> is not like VME

- **#2** How Signal Integrity can dramatically impact system performance

- \*3 The ways that Thermal Management can ruin your day and your program

- #4 The Game-Changing Impact of OpenVPX profiles

VPX is both a much higher performance platform than VME and is significantly more complex.

#### Why VPX Is Not Like VME?

One common error results when customers look at VPX and think that it's just like VME. The fact is that there are significant differences between the two architectures. It is true that, like VME, VPX targets rugged applications. But, VPX is both a much higher performance platform than VME and is significantly more complex. It is neither safe to assume that any given OpenVPX module is compatible with any randomly selected backplane/chassis, nor that the module will be compatible with another randomly selected module. The table below highlights a few key areas that illustrate critical differences between VME64x and VPX.

OpenVPX modules and backplanes need to be selected carefully to ensure compatibility. Atrenne Computing Solutions can help you select the right modules and backplanes for your application.

| Parameter                                | VME64x                                                    | OpenVPX                                                                                                                                                                                                                                                                                     |

|------------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Slot Pinout                              | All VME64x slots have the same pinout for VMEbus          | Multiple different OpenVPX slot profiles defined with different pinouts                                                                                                                                                                                                                     |

| Backplane<br>Communication               | 64-bit parallel<br>multi-drop bus                         | Multiple different serial fabrics defined for multiple different OpenVPX planes (data plane, control plane, expansion plane)                                                                                                                                                                |

| Backplane Topology                       | Bussed                                                    | Multiple different OpenVPX backplane profiles defined with different point-to-point serial connections, including both distributed types and central switched types                                                                                                                         |

| Backplane Speed                          | Multiple rates defined up<br>to 320 Mbytes per sec        | Multiple OpenVPX fabric rates defined up to 6.25 Gbaud per differential pair  - A 1x link (Ultra Thin Pipe) provides 2x higher data throughput in each direction than the entire VMEbus  - Most defined Data Plane links are 4x (Fat Pipe)  - Now adding Gen3 rates to 10.3 Gbaud or higher |

| Module and<br>Backplane<br>Compatibility | Any VME64x card can<br>be used in any VME64x<br>backplane | The Module's OpenVPX Module Profile must be compatible with Backplane's OpenVPX Slot Profile – same types of signals in the same locations                                                                                                                                                  |

|                                          |                                                           | OpenVPX Module Profile fabric types for multiple Modules used must be compatible with each other if they are connected on the backplane (e.g. PCIe on one Module cannot be connected to SRIO on another Module)                                                                             |

|                                          |                                                           | OpenVPX Module Profile's fabric baud rate must be compatible with Backplane's rated baud rate (e.g. backplane needs to be at least as fast as fabrics used)                                                                                                                                 |

# How Signal Integrity Can Dramatically Impact System Performance

OpenVPX requires a whole different level of attention to Signal Integrity. Failing to diligently address Signal Integrity can have serious consequences.

In comparison to OpenVPX, VME64x backplanes are relatively low-tech. Because they do not require gigabit type signaling, VME64x backplanes typically utilize high-loss FR-4 laminate types. The design of VME64x backplanes is also typically much simpler. For example, many backplane suppliers and system integrators have successfully developed and deployed VME64x backplanes without having to use sophisticated 3D modeling and simulation tools. While VME64x backplanes can have issues with crosstalk and power integrity if not properly designed, resolving these issues does not require sophisticated tools.

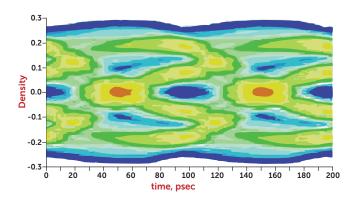

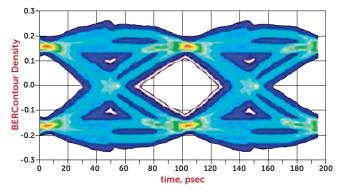

In contrast, OpenVPX requires a whole different level of attention to Signal Integrity. Failing to diligently address Signal Integrity can have serious consequences, such as high speed serial links that have high bit error rates, won't run at rated speeds (must negotiate down in speed), or in worst case, don't work at all! Signal Integrity problems can take a serious bite out of your system level performance!

To avoid these problems, Atrenne Computing Solutions' Hybricon® OpenVPX backplanes have always been designed with the highest signal integrity available in the industry. Because of OpenVPX's dramatically higher speed signaling attention has to be paid to very small but crucial details. This includes use of sophisticated 3D field solvers and simulation tools to ensure that the backplanes will operate at their rated speeds. Unfortunately, many backplane suppliers and system integrators just don't have the proper tools and expertise required to ensure successful high-speed OpenVPX communication with low bit-error rates.

To ensure the health of your payload and your program, you need to pay close attention to your backplane's signal integrity – to make sure that you are getting adequate signal integrity ask for evidence that the vendor's OpenVPX backplanes were designed to meet VITA 68 signal integrity budgets. Atrenne Computing Solutions can help you select the right backplanes with all of the performance that you need for your application.

**Figure 1:** VPX Interconnect Eye Diagram Without Equalization at 10.3 Gbaud

**Figure 2:** VPX Interconnect Eye Diagram With Equalization at 10.3 Gbaud

# The Ways That Thermal Management Can Ruin Your Day & Your Program

Inadequate thermal management can put your program's overall success at risk.

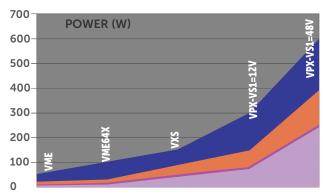

Compared to OpenVPX, VME64x modules are relatively low power and require only modest cooling; as a result, thermal management is typically not one of the biggest concerns for a VME system.

Many chassis suppliers and system integrators have successfully developed and deployed VME64x chassis without the use of sophisticated thermal modeling and simulation tools, because typical VME64x modules don't consume a lot of power.

A really hot VME64x module might top out at about 60W. In comparison, for a 6U OpenVPX module, 60W is relatively low power. It's not unusual for hot OpenVPX modules to consume 2 to 3 times as much power!

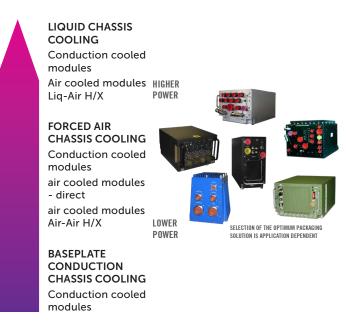

Because OpenVPX modules typically operate at much higher temperatures than VME cards, they require much greater attention to Thermal Management. Failure to do so can result in burning up an expensive set of payload modules due to inadequate cooling. Needless to say, inadequate thermal management can put your program's overall success at risk. As with Signal Integrity, many chassis suppliers and system integrators just don't have the proper tools and expertise required to ensure successful thermal management of hot OpenVPX payloads.

Be especially concerned about thermal management when a OpenVPX backplane is being installed into a chassis that was designed for VME64x. Otherwise, the result can be disastrous.

For the health of your payload and your program, you need to ensure that your chassis has adequate cooling! Atrenne Computing Solutions can help you select the right chassis with the performance that you need for your application.

- Actual 6U VXs modules typically 100W

- Some Hot 6U VXS modules > 150W

- Actual 6U VPX Multiprocessor / DSP Module Power is typically -125W

- Some Hot 6U VPX modules 200W

- Actual 3U VPX Multiprocessor / DSP Module Power is typically -75W

- Some Hot 3U VPX modules > 100W

Figure 3: New Boards are Getting Hotter

Figure 4: Chassis Mechanical and Cooling Options

To ensure success, the OpenVPX system interconnect needs to be planned out, and compatible modules and backplanes need to be selected (or developed).

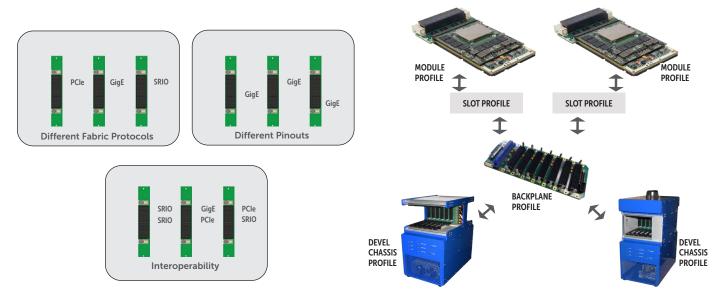

#### The Game-Changing Impact Of OpenVPX Profiles

In the halcyon days when VME was ascendant, any VME64x card could be used in any VME64x backplane. Even better, all of the VME64x slots had the same pinout for the VMEbus. This made life relatively simple, as a VME chassis could often be used for numerous different applications with different payloads.

With OpenVPX that paradigm is no longer true, and the difference for system designers is game-changing. Many OpenVPX backplanes have slots with different pinouts (e.g. payload slots and switch slots), and different OpenVPX backplanes can have slot pinouts that are different from each other (these are called Slot Profiles).

OpenVPX Modules are compatible with one or more Module Profiles. When selecting a compatible backplane, that Module Profile must be compatible with the Backplane Slot Profile. Also, Module Profile fabric types when using multiple modules must be compatible with each other if they are connected on the backplane. For example, PCI Express® on one module cannot be connected to Serial RapidIO® on another module. In addition, the module Profile's fabric baud rate must be compatible with the backplane baud rate. That means that the backplane must be designed to run at least as fast as the speed of the module's fabrics. These issues are a world away from the concerns that face the designer of a VME system. To ensure success, the OpenVPX system interconnect needs to be planned out, and compatible modules and backplanes need to be selected (or developed). The simple fact is that there is no such thing as a "generic OpenVPX backplane" that is suitable for all applications. With OpenVPX, backplane selection is application dependent.

Figure 5: VPX Interoperability

Figure 6: OpenVPX Profile Framework

General Inquires: +1 800 926 8722

Atrenne Computing Solutions, US: +1 508 588 6100

sales@atrenne-cs.com | atrenne.com

All photos used are for reference purposes only. The appearance of U.S. Department of Defense (DoD) visual information does not imply or constitute DoD endorsement.

© Atrenne Computing Solutions LLC, 2025 All rights reserved. Atrenne & Design are existing, pending or registered trademarks of Celestica Inc. or its subsidiaries or used under license. All pending and registered trademarks are the property of their respective owners.